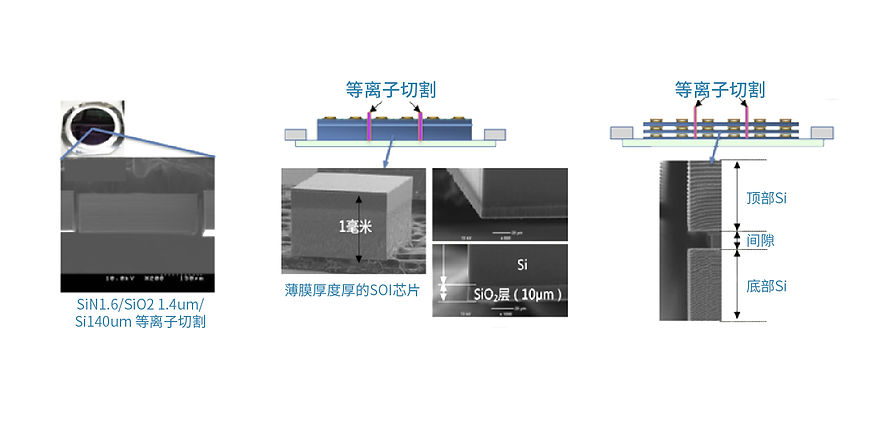

Plasma 切割方案

内容介绍

传统锯片或激光切割的可行替代方案 – 正在进入第三代半导体SiC领域

并行处理:“高芯片密度下极高”的切割效率和效益

最小的切割道:提升单晶圆上的芯片产量(最多增加80%)

极高的性能上限:超薄晶圆(30um)、边缘处理和低损伤

高度配合晶圆设备,提供更大的工艺灵活性, 晶圆级先进封装

新型切都应用的书最超汇化的趋势及应对方案:

一.趋势和原因

1.晶日度的变化进程:

1. 常规 12 寸星日,在经过满薄后大约是 280 微米- 400 微米

2. 超薄化的晶园 -- 100um 以下 :常规用于疊层封装的滅導到100 微米以下,更为先进的封装要到50 。

3.最新: 目前最薄的 wafer 已经发展到30 微米的厚度,适应25D-3DIC 以及 先进存储等 多层难暨封装的需求。

2.晶同超靠化的原因:

1.核心是配合先进封装的要求,复杂的封装,但是不能过多牺性 xy和z轴上的尺寸,因此在尺寸有极眼的情况下,多样化的封装技术(PIP(packagein package层封装),POP(packag e onpackage)、多芯片、系统级封装以及 2.5-3D封装等),都要求星周尽量变薄,给封装工艺留下更多的空间.

2.减薄减少芯片内部的应力,大大降低因为内力导致芯片破烈的情况,这样封装后处处理更容易,特别是涉及到异质和异构集成时候,,不同芯片的应力差和晶格失配,导致的剪切力,致使芯片崩碎是最难解夫的问题。

3.电气性能的提高:减小了封装体积同时提害了电路性能,减小了高生效应和时间延迟

4.增加散热, 衬底片薄了,更容易把热导出去,特别是芯片结构更加复来,集成度更高,导致的热:聚集快不容易疏散的特点

二.减萍后问题

1.物理特性的改变:

品同的过分减藏,会号致物理刚性的降低,重力作用下就会发生很大的变形卷曲,会在做动气流中发生振:边缘的物理碰撞部极易损坏,具有锋利的边缘,会与其他平面粘合在一起而难分开

2.后道工字和搬运的难度会大,对于传输和史具的要求推高:

1.边缘损伤是所有切割方案里最小的,最适于对损伤高度敏感的场景

反应离子刻蚀,物理和化学变化结合,边缘处理是个方法最好的,在微米级别不会有毛刺,对芯片的可能损伤是最小最小的。

先进制程的芯片,且使用了很多铜(Cu)或低介电常数等材料(Low-k )。因此,为了防止毛刺(Burr)的重要性就更重。后续在2.5D-3D封装,特别是技术发展中的CHIPLET, 这将是一个更具有竞争力的方案。

2. 50微米以下,最低到30微米的超薄晶圆

需要用到离子体切割,而 激光方案可能无法渗透到这一领域(50-100um厚度比较擅长),再往下可能不太行了,他斜裂的影响可能就大了。

3. Dicing street 切割街道,拥有最小的极限值

等离子体切割所形成的切割道的理论极限值是最小的,可以轻松做到亚微米级别,可以大幅度的降低切割损耗。但是要看具体的材料和要求。根据测算 可以多出来20%的芯片量。 节省成本

4.速度上,单晶元并行处理,可以有极高的速度

一次性切割完毕,效率是高的。但是要考虑芯片的厚度,厚了也非常难切割,时间也不会太快。考虑厚芯片不是主要的一个应用方向应该。

5. 可以和晶圆工艺设备深度协同

光刻+刻蚀的图形化方案越来越普遍, 用等离子体切割拥有非常良好的设备平台,而不需要单独加入 SD激光切割设备和裂片机。 并且,先进封装成本越来越高,堆叠要求越高,制造和封装的深度协同,让封装前的前道工艺的精细化处理就更有意义。